An Analogy: How much noise is noisy?

It is a bit like teaching in a classroom full of students. To what extent does the noise level of students chatting becomes sufficiently noisy to interfere with the teaching? Memory systems always have some degree of electrical noise and uncertainties as no two environments are identical.Generally, every progressive generation of DDR memory has less tolerance for signal uncertainties. Memory stability problems are usually a matter of motherboard engineering and BIOS optimisation. In short, it is a bit like everyone in the class talking faster and faster. Any unusually loud noise will cause everyone to lose track of the conversation easier, opposed to talking slower, because they can't hear what's being said. Of course, this is a simple take on a complex issue.

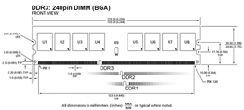

DDR DIMM (Module) Identification

Almost all generations and types of memory have slightly different dimension, pin configuration and notch-key location to avoid inter-generation confusion between modules and sockets.The majority of desktop motherboards manufactured today only support a single type of memory, but there are rare exceptions that work with both Unbuffered and Registered DIMMs. The JEDEC standard does provide accommodation for motherboards that are capable of working with either U-DIMM or R-DIMM, but not both at the same time. As a result, Unbuffered and Registered DIMMs share the same interface and key location.

Evolution of DDR Topology

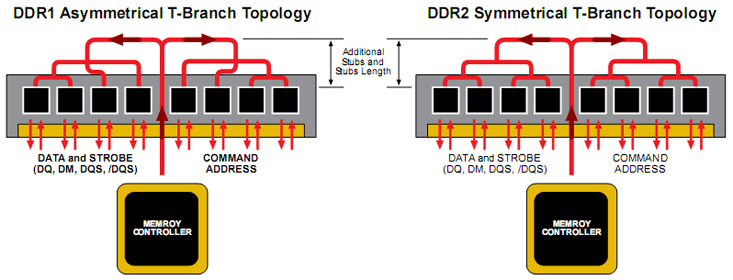

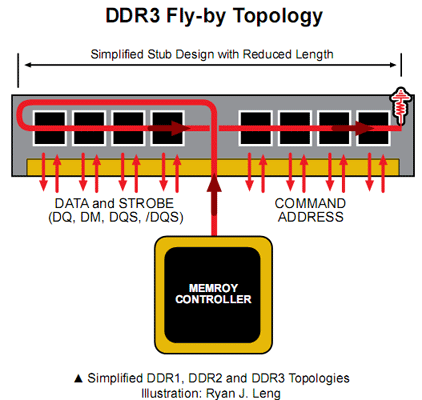

Topology design plays an important role in maintaining healthy signalling characteristics along the memory pathways. It is commonly known among memory engineers (although not exclusive to memory) that when the memory performance increases, the signals become more susceptible to error. To mitigate and reduce the adverse effects of faster memory, every generation of computer RAM requires a new design. Better electrical signalling properties are achieved by simplifying and shortening the data conduit.

Because each generation of DDR has these degrees of signal problems, as long as the memory performance is maintained below a certain maximum range, such as DDR2 800MHz, it is unlikely stability problems will be encountered. Topology is a very important aspect of DDR3: its fly-by topology signalling delay is very predictable, hence can be very easily tuned and compensated for. DDR2 Symmetric T-Branch multi-stubbed design can readily cause unpredictable "shakiness" in the signal that is much harder to fix at higher speeds.

Something that has yet to fully realized is the actual reliability of DDR3-1600 and beyond. Based on my personal work though, DDR3 is significantly more reliable at very high speeds, after all we already have 1,800+MHz modules permeating the market just six months after the products introduction.

Registered DDR3 has a slightly different topology to even Unbuffered DDR3, which we will also cover later.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.